To tylko jedna z 8 stron tej notatki. Zaloguj się aby zobaczyć ten dokument.

Zobacz

całą notatkę

Wydział Elektroniki Politechniki Wrocławskiej

Laboratorium Przyrządów Półprzewodnikowych

Wykonał Pirosz Paweł

Andrzej Pieliński Grupa 9

Ćw. nr 3

Prowadzący dr Bober

Badanie właściwości układów cyfrowych CMOS

Data wykonania 99.05.19

Data oddania 99.05.26

Ocena PROGRAM ĆWICZENIA :

1. Sprawdzenie poprawności działania układu CMOS

2. Pomiary charakterystyk statycznych

charakterystyk wyjściowych UOL = f(IOL) w stanie „0” na wyjściu

charakterystyk wyjściowych UOH = f(IOH) w stanie „1” na wyjściu

charakterystyk przejściowych UO = f(UI) 3. Pomiary czasu propagacji bramek CMOS

4. Pomiary mocy pobieranej ze źródła zasilania w funkcji napięcia zasilania i częstotliwości oraz rodzaju obciążenia bramki elementami RC.

WYKAZ PRZYRZĄDÓW :

Zasilacz napięciowy ZLS-3

Oscyloskop Hewlet Packard

Multimetr cyfrowy V560

Rejestrator XY

Obciążenie aktywne

Układ scalony MCY74011

PARAMETRY UKŁADU SCALONEGO CMOS MCY 74011:

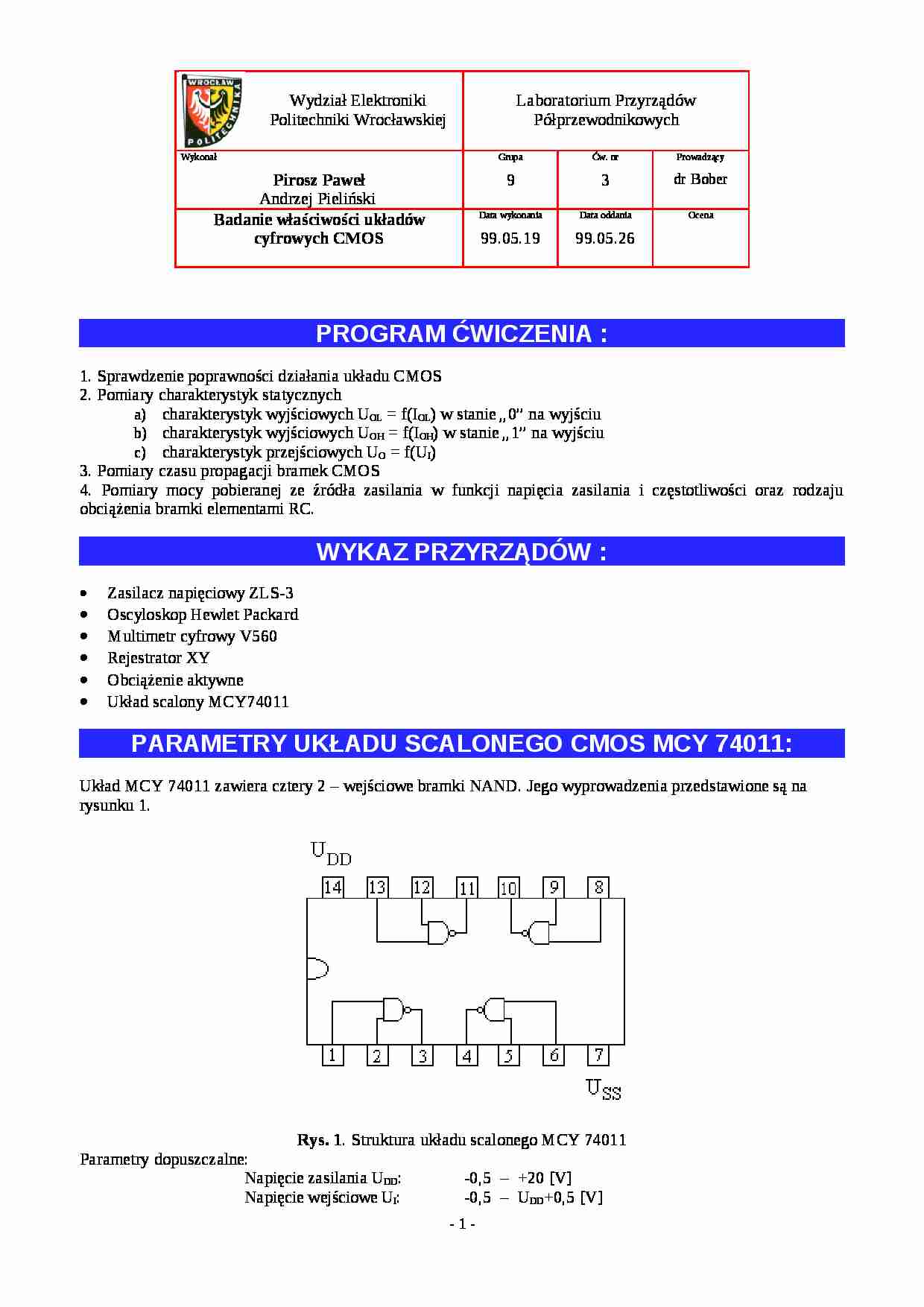

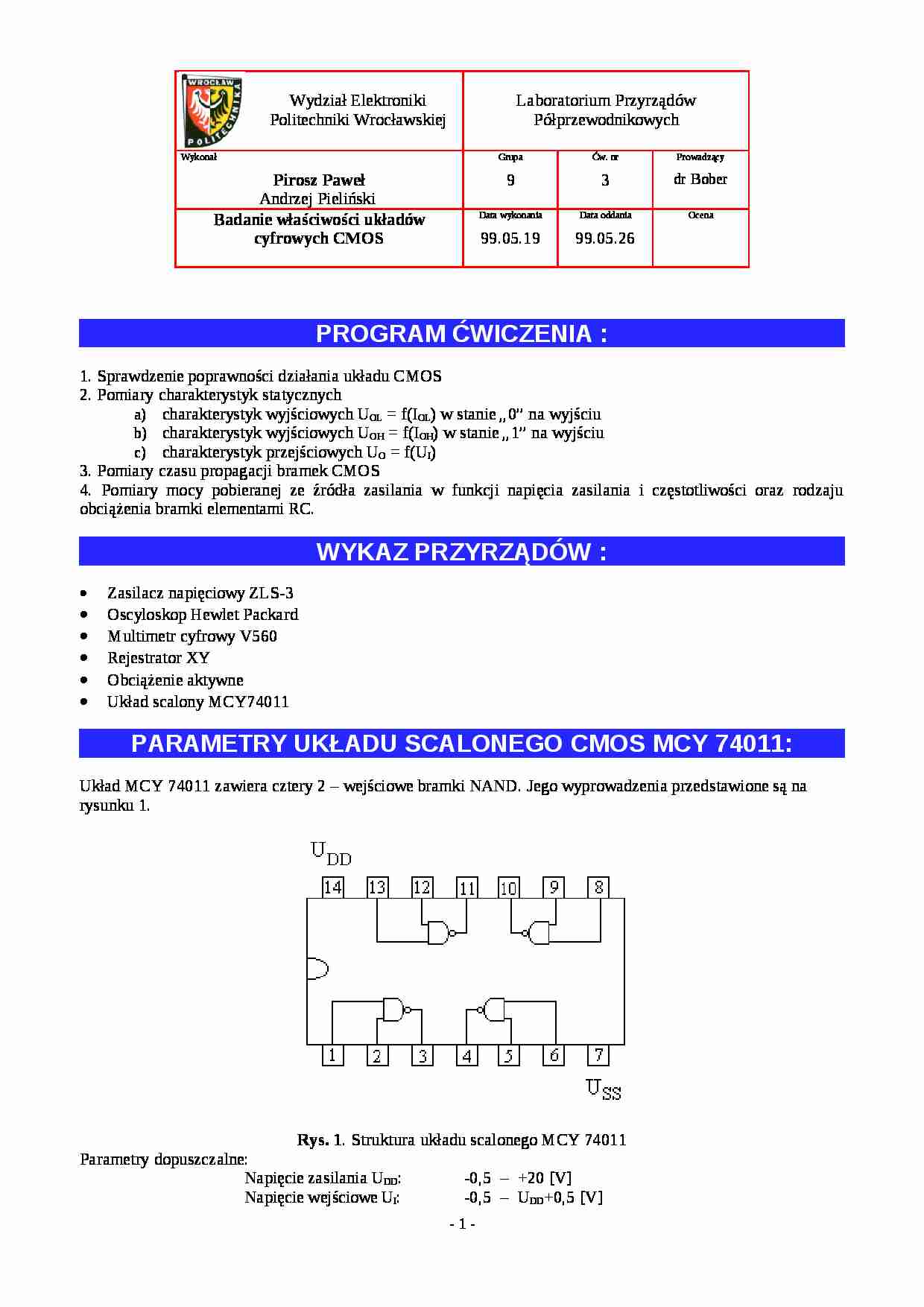

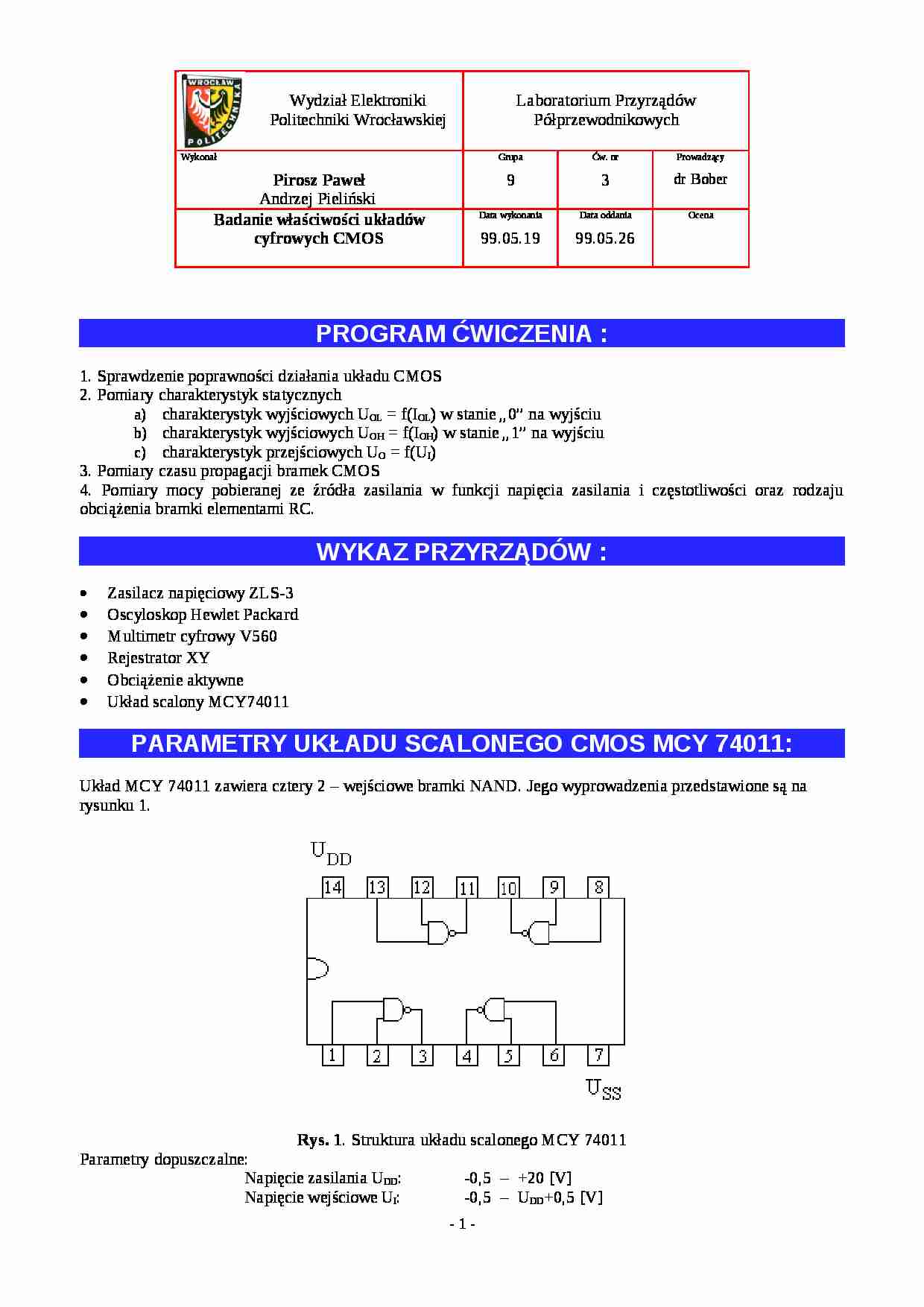

Układ MCY 74011 zawiera cztery 2 - wejściowe bramki NAND. Jego wyprowadzenia przedstawione są na rysunku 1.

Rys. 1. Struktura układu scalonego MCY 74011

Parametry dopuszczalne:

Napięcie zasilania UDD: -0,5 - +20 [V]

Napięcie wejściowe UI: -0,5 - UDD+0,5 [V]

Prąd wejściowy II: -10 - +10 [mA]

Moc rozpraszana PD: 500 [mW]

Parametry charakterystyczne statyczne:

Napięcie wyjściowe w stanie wysokim UOH: UDD-0,5 - UDD [V]

Napięcie wyjściowe w stanie niskim UOL: 0 - 0,05 [V]

Prąd wejściowy II: ±10-5 - ±1 [A]

Parametry charakterystyczne dynamiczne (CL = 50pF, RL = 200k):

Oznaczenie

Nazwa

Jedn.

Wartość

Warunki pomiaru

UDD [V]

typ

max

tPLH Czas propagacji zmiany stanu z niskiego na wysoki

[ ns ]

125

60

45

250

120

90

5

10

(…)

… UOL = f(IOL) dla napięć zasilania UDD = 5, 10, 15 [V] przedstawione są na wykresie 1.

Ponieważ oś X skalowana jest napięciem 20mV/cm, zatem prąd jaki przepływa przez opornik o wartości 10Ω - prąd IOL - jest skalowany, zgodnie z prawem Ohma, wartością 2 mA/cm. Napięcie UOL - oś Y - jest skalowane 1V/cm.

Na podstawie wykresu 2 wyznaczono rezystancje dynamiczne bramki CMOS zgodnie ze wzorem:

.

Otrzymane…

... zobacz całą notatkę

Komentarze użytkowników (0)