Przedstaw budowę i zasadę działania inwertera CMOS.

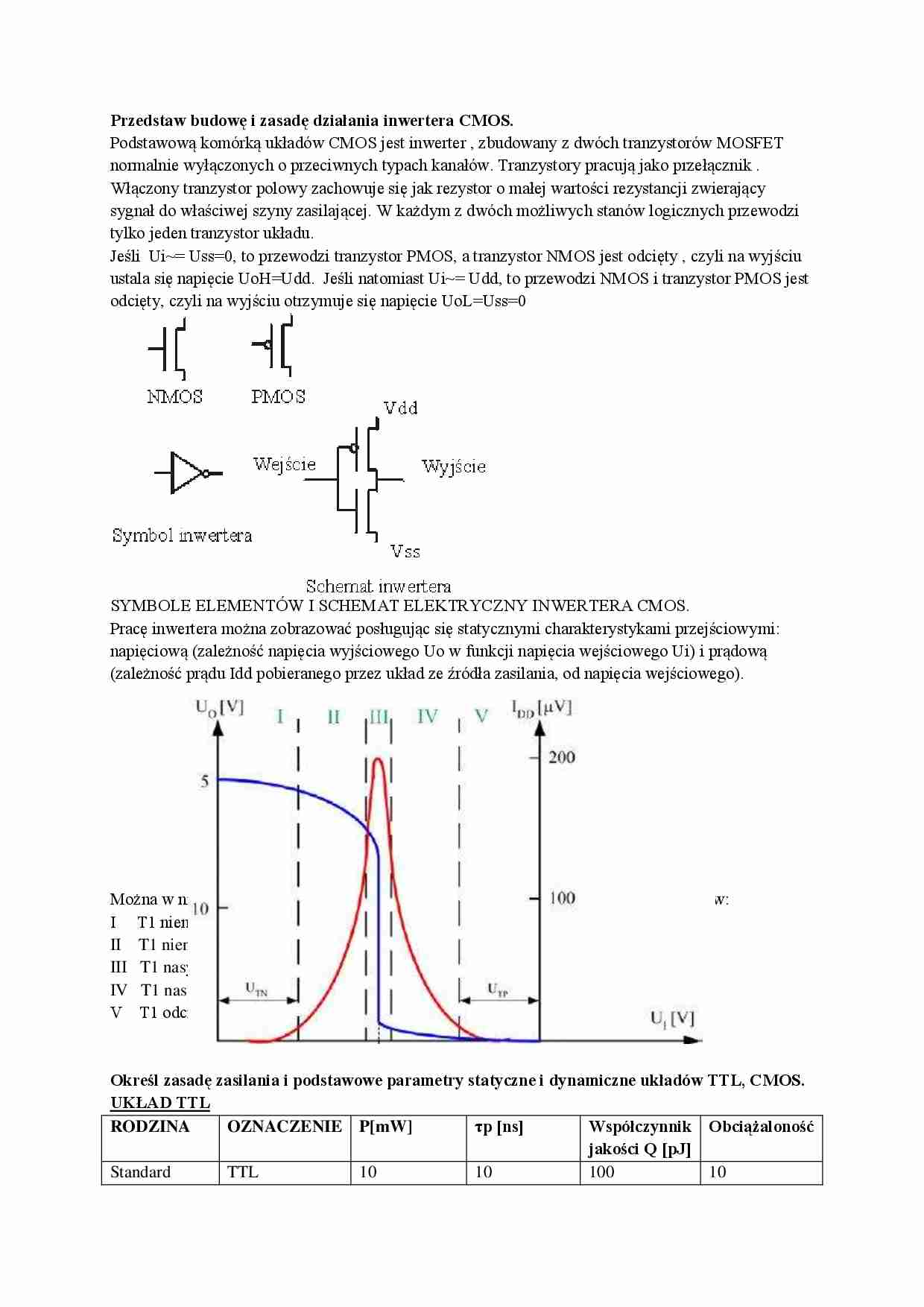

Podstawową komórką układów CMOS jest inwerter , zbudowany z dwóch tranzystorów MOSFET normalnie wyłączonych o przeciwnych typach kanałów. Tranzystory pracują jako przełącznik . Włączony tranzystor polowy zachowuje się jak rezystor o małej wartości rezystancji zwierający sygnał do właściwej szyny zasilającej. W każdym z dwóch możliwych stanów logicznych przewodzi tylko jeden tranzystor układu. Jeśli Ui~= Uss=0, to przewodzi tranzystor PMOS, a tranzystor NMOS jest odcięty , czyli na wyjściu ustala się napięcie UoH=Udd. Jeśli natomiast Ui~= Udd, to przewodzi NMOS i tranzystor PMOS jest odcięty, czyli na wyjściu otrzymuje się napięcie UoL=Uss=0 SYMBOLE ELEMENTÓW I SCHEMAT ELEKTRYCZNY INWERTERA CMOS.

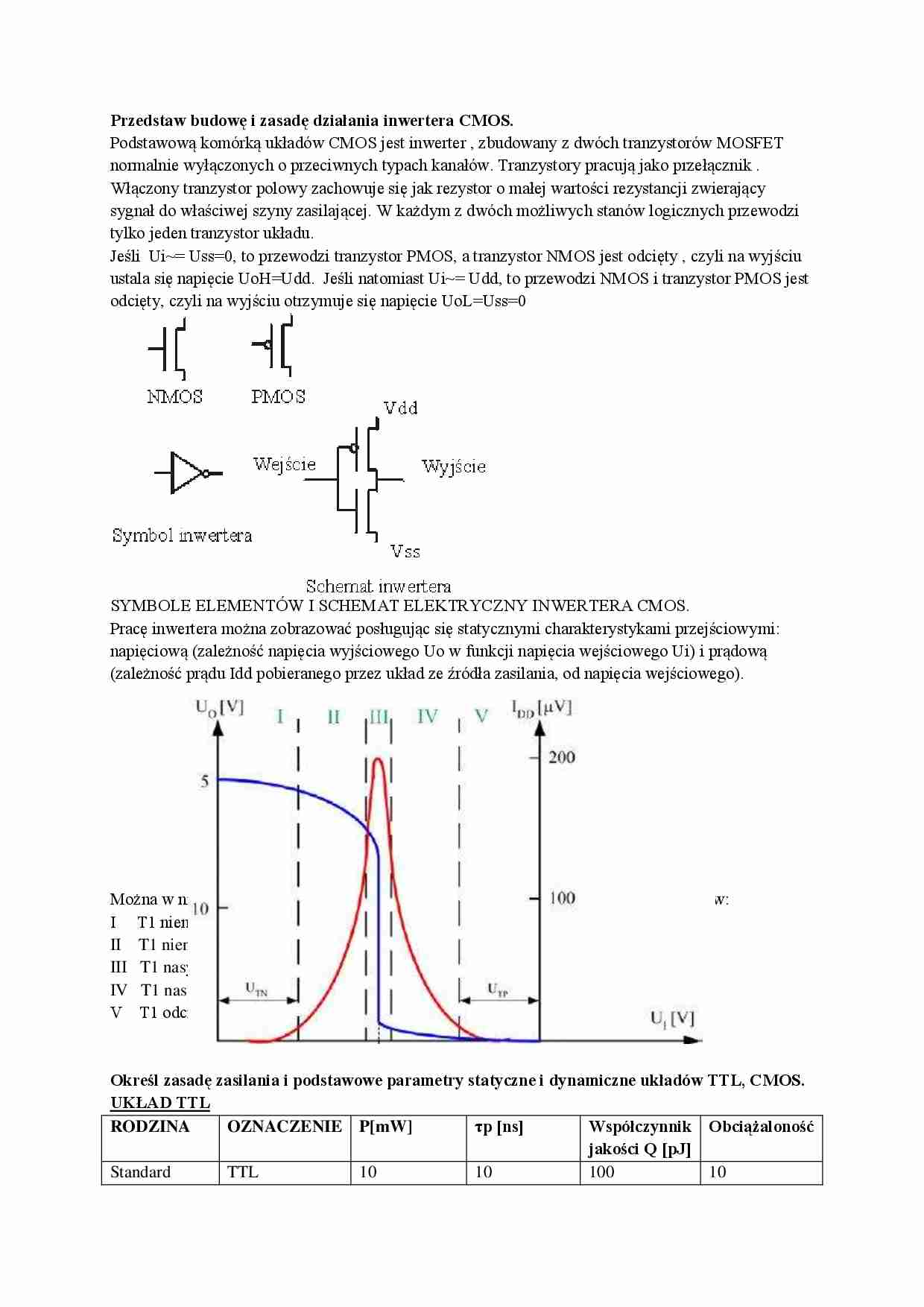

Pracę inwertera można zobrazować posługując się statycznymi charakterystykami przejściowymi: napięciową (zależność napięcia wyjściowego Uo w funkcji napięcia wejściowego Ui) i prądową (zależność prądu Idd pobieranego przez układ ze źródła zasilania, od napięcia wejściowego).

Można w nich wyróżnić pięć obszarów określonych przez różne tryby pracy tranzystorów:

I T1 nienasycony, T2 odcięty

II T1 nienasycony, T2 nasycony

III T1 nasycony, T1 nasycony

IV T1 nasycony, T2 nienasycony

V T1 odcięty, T2 nienasycony

Określ zasadę zasilania i podstawowe parametry statyczne i dynamiczne układów TTL, CMOS.

UKŁAD TTL

RODZINA

OZNACZENIE

P[mW]

τp [ns]

Współczynnik jakości Q [pJ]

Obciążaloność

Standard

TTL

10

10

100

10

Advanced Schottky

TTL AS

8

1,7

13,6

48

Adv. Low Power

TTL ALS

1,2

4

4,8

40

FAST

TTL F

5,5

3,5

19

33

Wszystkie układy TTL zasilane są napięciem 5V±5% (5V±10%- układy 54xx)

Napięcia stanów logicznych:

Stan niski (0)- to napięcie 0,2 V (przedział: 0V- 0,4 V)

Stan wysoki(1)- to napięcie 3,5 V (przedział 2,4 V- 5 V)

UKŁAD CMOS

RODZINA

OZNACZENIE

Ucc[V]

τp [ns]

fpracy[MHz]

Z bramką MOS metalową

4000B (74C)

3- 18

125

(…)

…,(AHCT)

5

3(5,2)

160 (115)

Niskonapięciowe

LV

2- 5,5

9

70 Zaawans. niskonapięciowe

ALVC

1,2- 3,6

3

300

Ponieważ moc tracona jest proporcjonalna do kwadratu napięcia zasilania układy CMOS VLSI dostosowane są do niższego napięcia zasilania: 3,3 V lub 2,5 V.

Układy CMOS o małej szybkości działania zasilane z baterii mają obniżone napięcia zasilania, nawet do 0,8 V- 1,5 V.

Układy serii 4000B (74C) pozwalają na pracę w szerokim zakresie napięć zasilania 3- 18 V i znajdują zastosowanie w warunkach dużych zakłóceń zewnętrznych.

Określ podstawowe parametry statyczne i dynamiczne (napięcie zasilania,

stany logiczne, charakterystyka przejściowa, moc tracona, czasy propagacji)

układów TTL i CMOS.

Napięcie zasilania - Wartość napięcia przyłożonego do układu, wymagana do podłączenia i sprawnej pracy układu…

… tracona = P(statyczna - tracona w czasie pracy ustalonej 0 lub 1) + P(dynamiczna - zależna od szybkości przełączania układu). Pomiędzy czasem propagacji i mocą strat istnieje zależność P - rośnie, Tp - maleje. Czas propagacji - Czas upływający od czasu zmiany stanu wejścia układu logicznego do chwili ustalenia się stanu wyjścia tego układu (reakcja na zmianę wejścia). Wskazuje na ograniczenie szybkości…

… = 10

Porównaj układy cyfrowe wytwarzane w technologii TTL i CMOS. 1. Układy CMOS nie mają stałego progu przełączania (jest ustalany procentowo), jak ma TTL 1,3 V.

2. Układy CMOS w przeciwieństwie do TTL w stanie statycznym nie pobierają prądu, jednak w trakcie zwiększania częstotliwości zwiększa się moc pobierana przez układ. 3. Moc pobierana przez TTL jest niezależna od częstotliwości i jest ciągle…

... zobacz całą notatkę

Komentarze użytkowników (0)