To tylko jedna z 4 stron tej notatki. Zaloguj się aby zobaczyć ten dokument.

Zobacz

całą notatkę

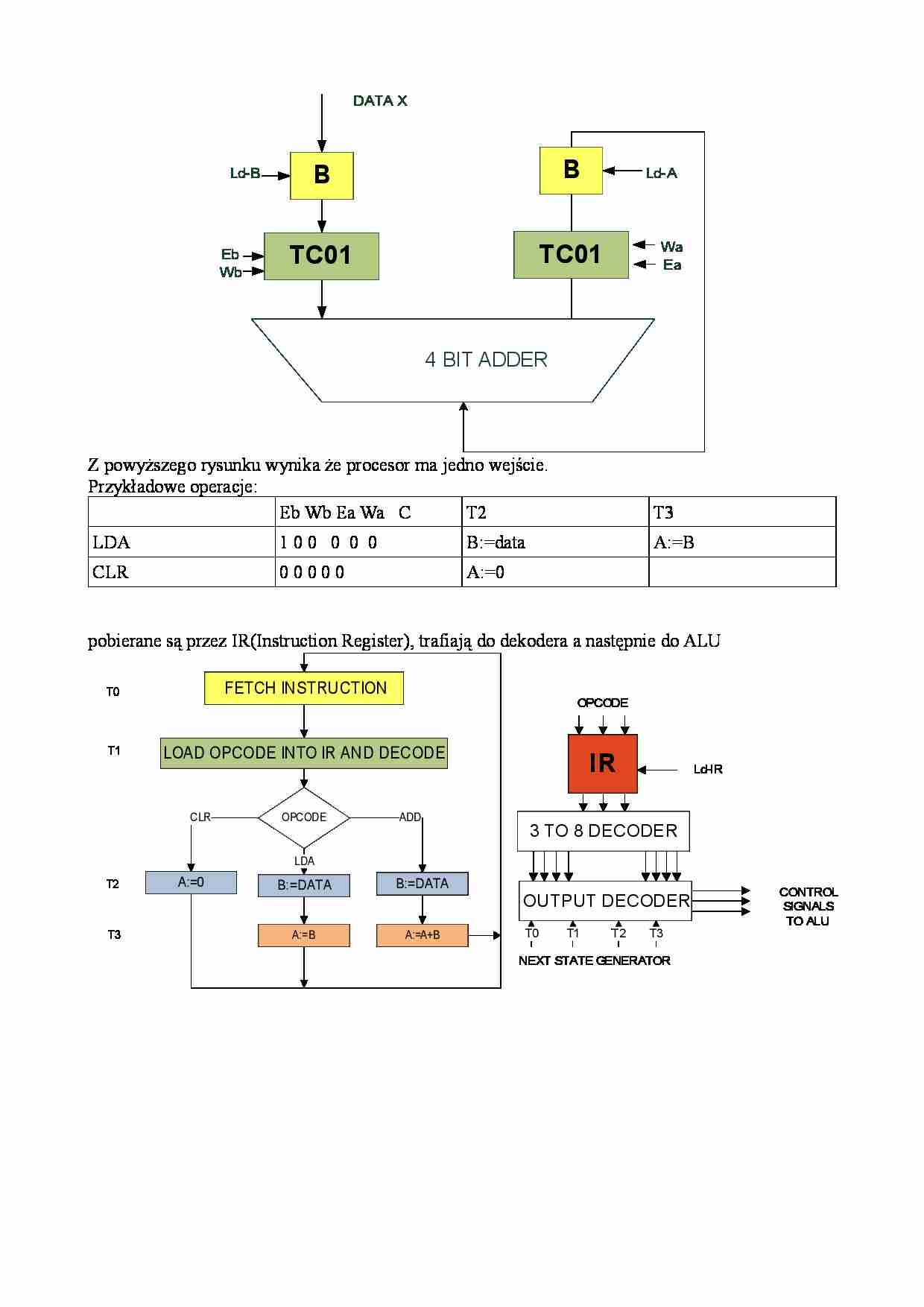

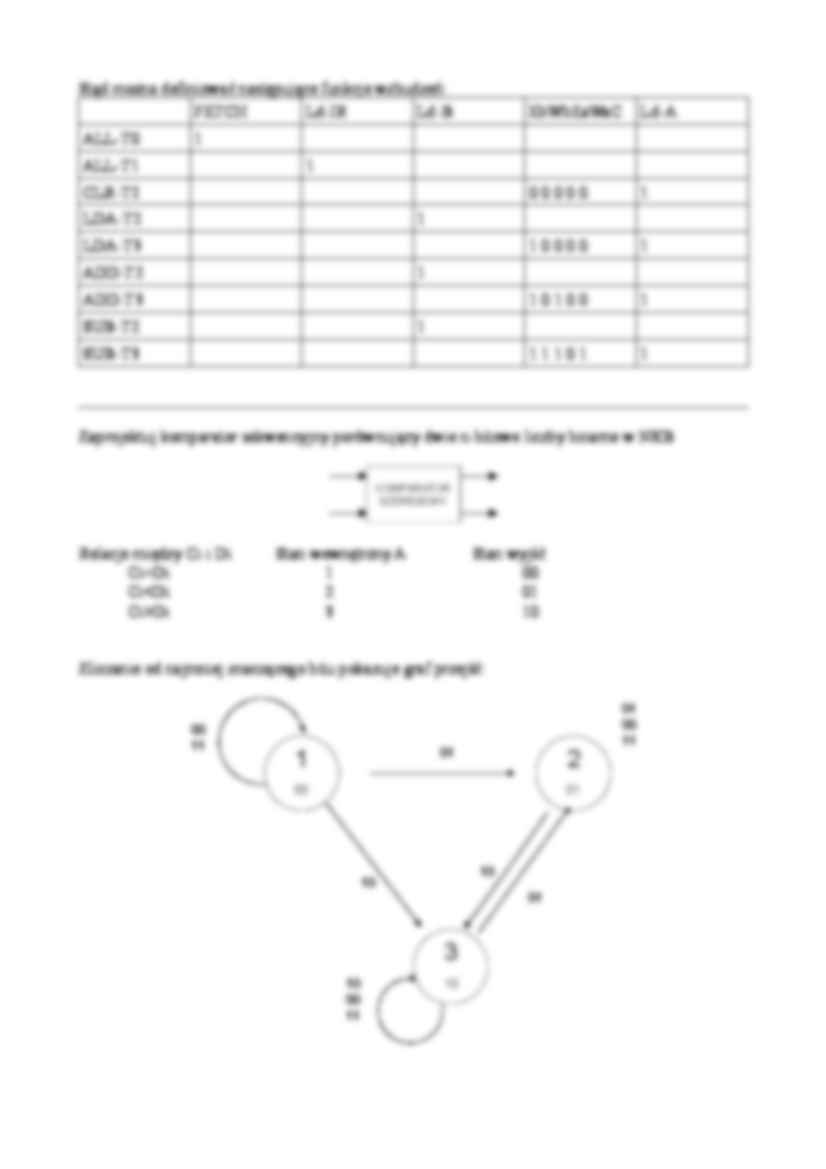

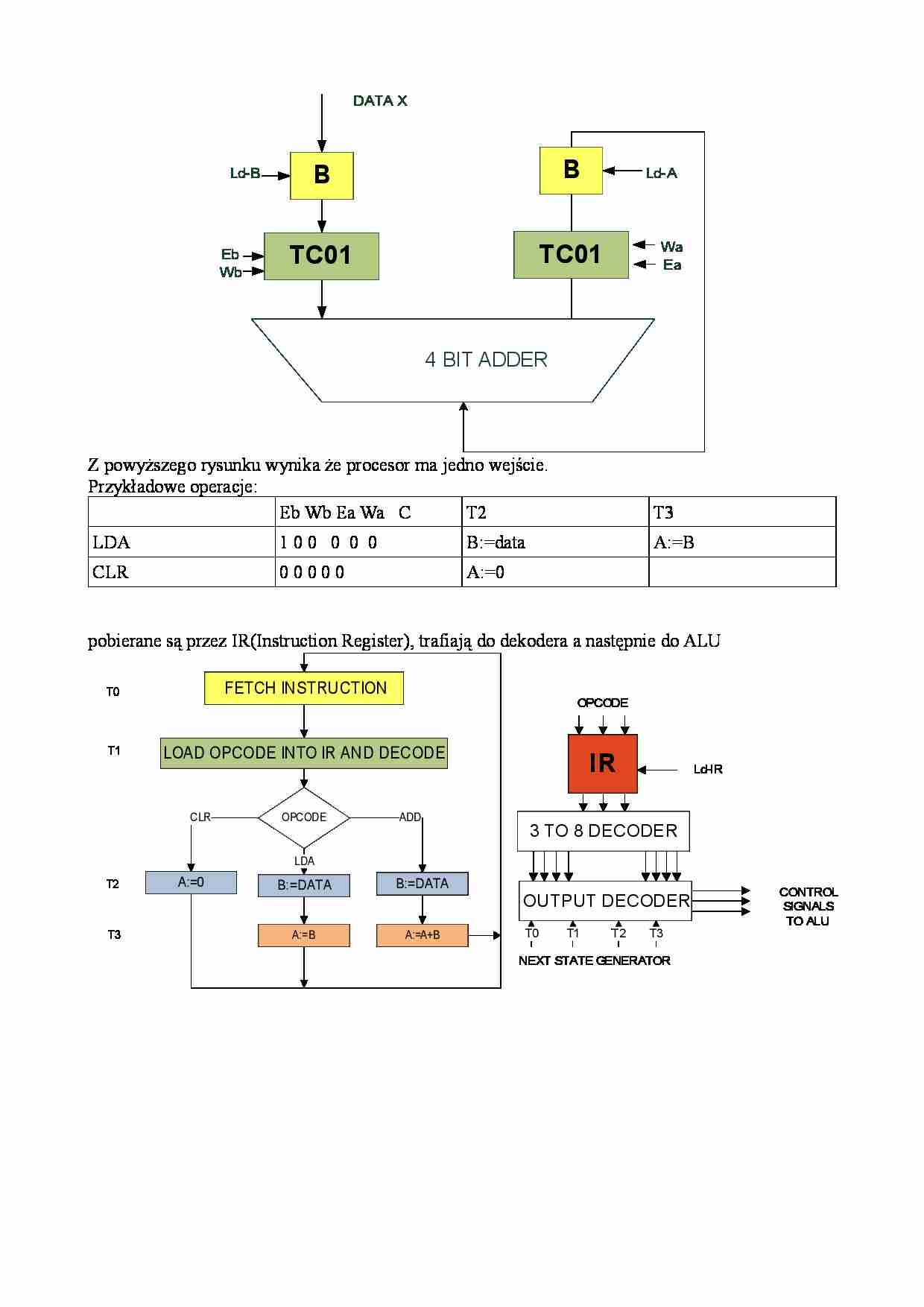

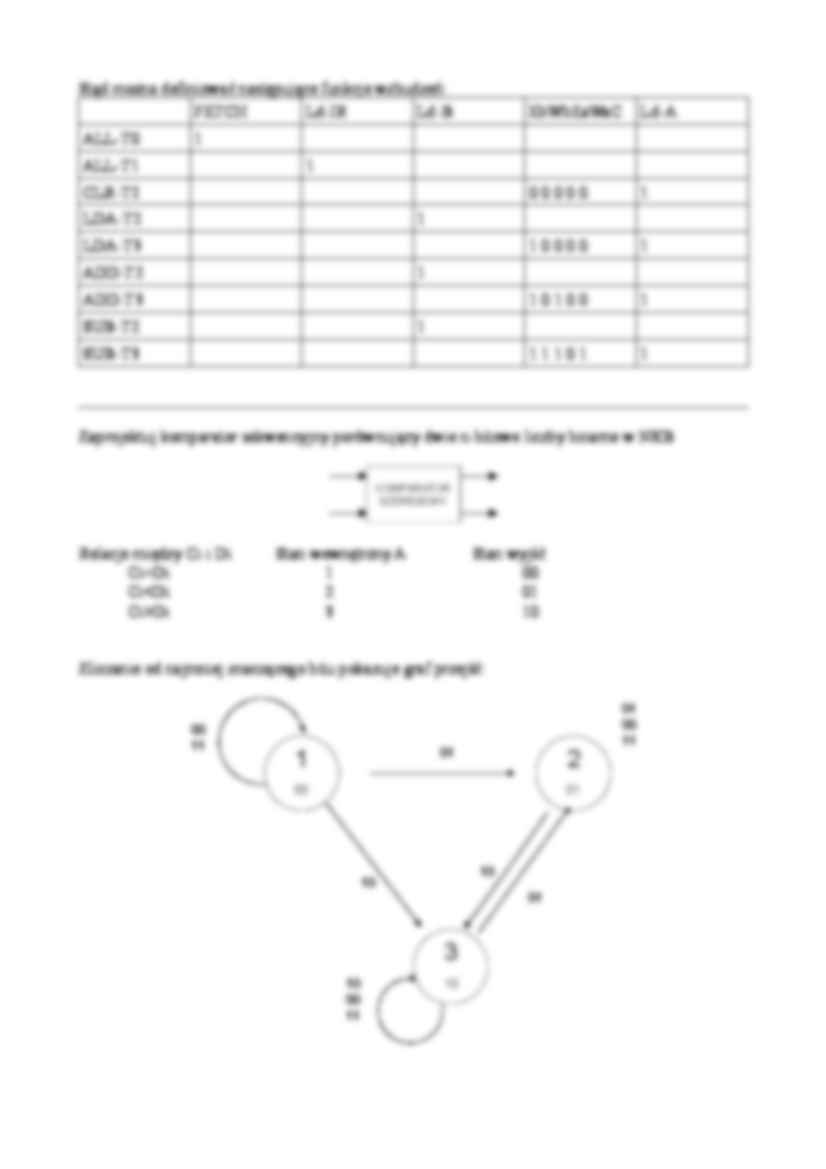

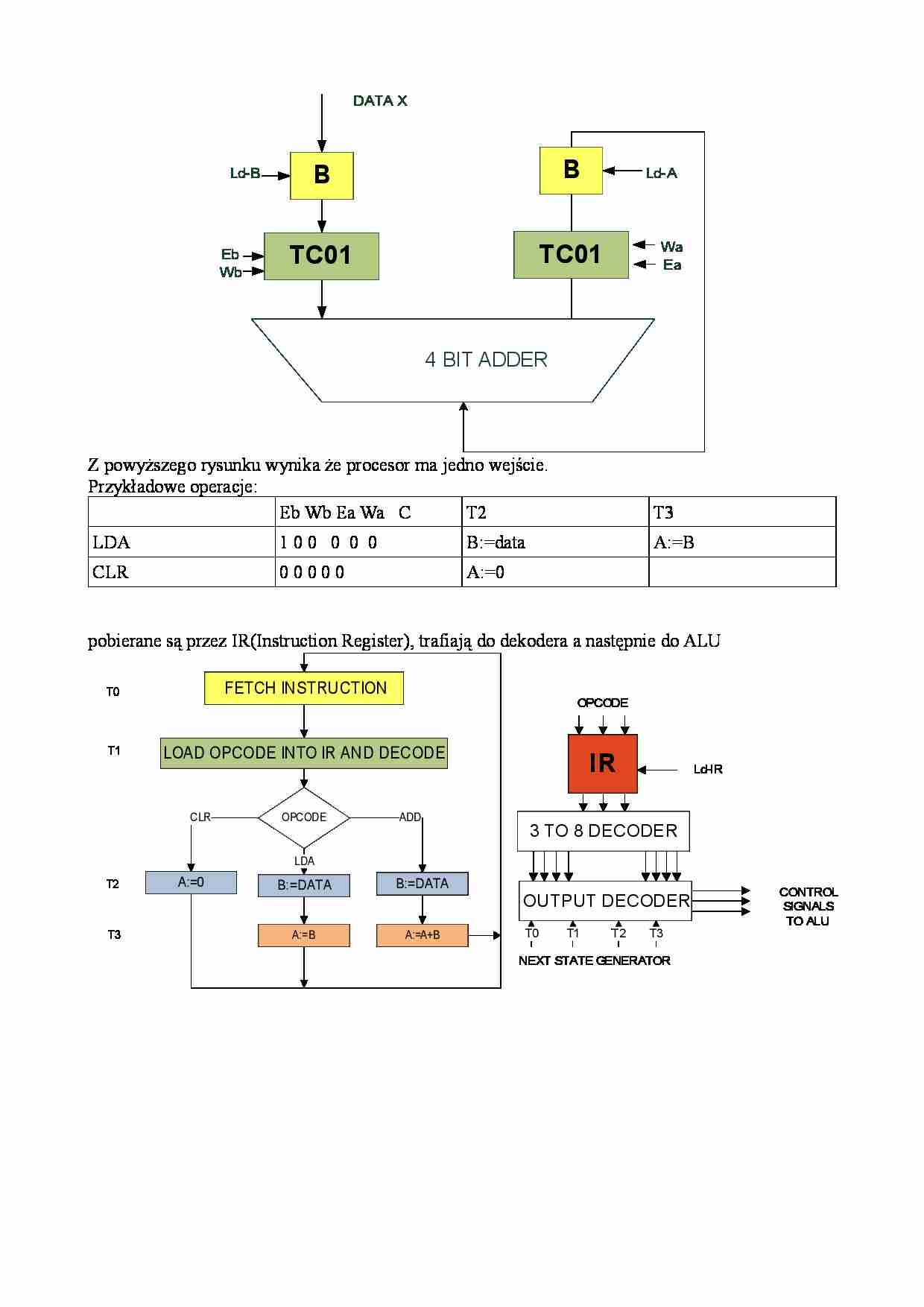

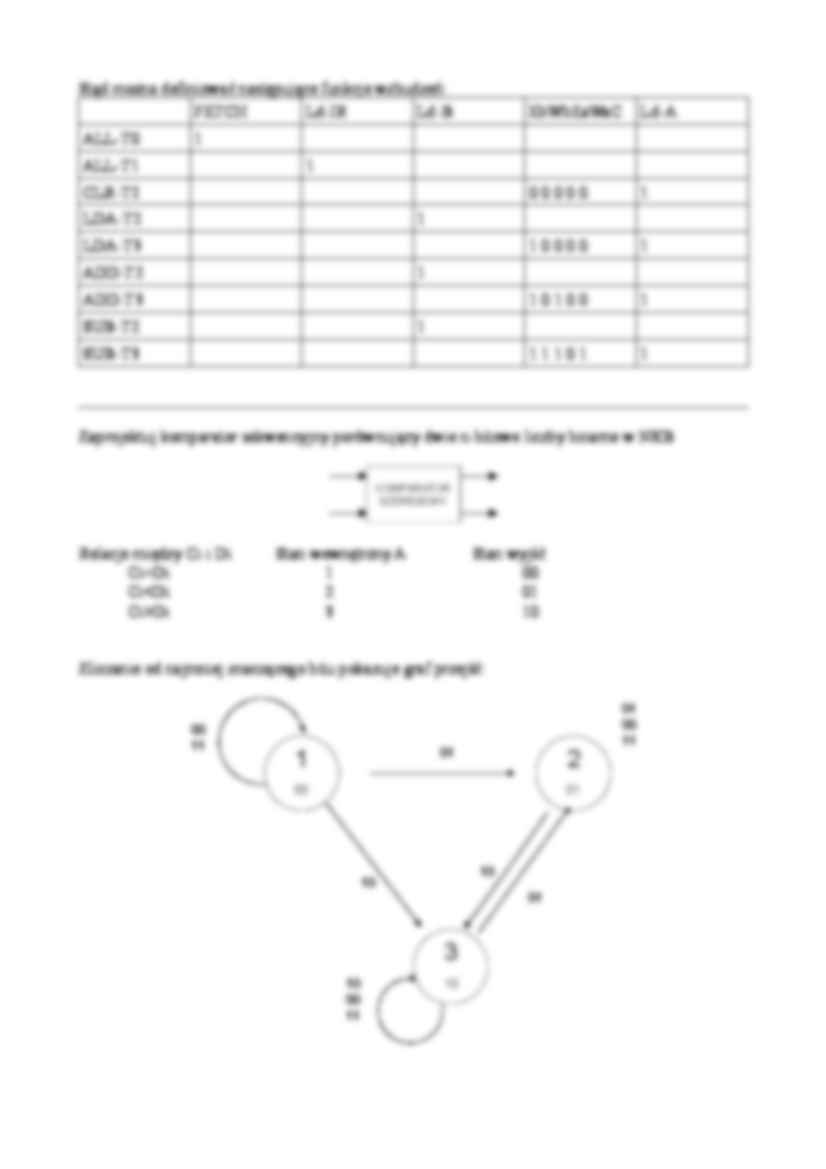

Z powyższego rysunku wynika że procesor ma jedno wejście. Przykładowe operacje: Eb Wb Ea Wa C T2 T3 LDA 1 0 0 0 0 0 B:=data A:=B CLR 0 0 0 0 0 A:=0 pobierane są przez IR(Instruction Register), trafiają do dekodera a następnie do ALU 4 BIT ADDER B B TC01 TC01 Wa Ea Eb Wb Ld-B Ld-A DATA X FETCH INSTRUCTION LOAD OPCODE INTO IR AND DECODE OPCODE A:=0 B:=DATA B:=DATA A:=A+B A:=B LDA CLR ADD T0 T1 T2 T3 IR 3 TO 8 DECODER OUTPUT DECODER OPCODE T0 T1 T2 T3 NEXT STATE GENERATOR CONTROL SIGNALS TO ALU Ld-IR Stąd można definiować następujące funkcje wzbudzeń: FETCH Ld-IR Ld-B EbWbEaWaC Ld-A ALL-T0 1 ALL-T1 1 CLR-T2 0 0 0 0 0 1 LDA-T2 1 LDA-T3 1 0 0 0 0 1 ADD-T2 1 ADD-T3 1 0 1 0 0 1 SUB-T2 1 SUB-T3 1 1 1 0 1 1 Zaprojektuj komparator sekwencyjny porównujący dwie n-bitowe liczby binarne w NKB Relacje między Ci i Di Stan wewnętrzny A Stan wyjść Ci=Di 1 00 CiDi 3 10 Zliczanie od najmniej znaczącego bitu pokazuje graf przejść: KOMPARATOR SZEREGOWY 1 00 2 01 3 10 01 10 10 10 00 11 01 00 11 00 11 01 Zliczanie od najbardziej znaczącego bitu pokazuje graf przejść: Pierwszy graf daje taka tablice przejść: x1x2(A) 0 0 0 1 1 1 1 0 y1y2 1 1 2 1 3 0 0 2 2 2 2 3 0 1 3 3 2 3 3 1 0 która w strukturze Mealy'ego ma postać: x1x2(A) 0 0 0 1 1 1 1 0 1 1\0 0 2\0 1 1\0 0 3\1 0 2 2\0 1 2\0 1 2\0 1 3\1 0 3 3\1 0 2\0 1 3\1 0 3\1 0 Zaś kodowanie tablicy przejść w celu realizacji układu za pomocą przerzutnika D wygląda następująco: Q1Q2 x1x2(A) 0 0 0 1 1 1 1 0 y1y2 1(00) 0 0 0 1 0 0 1 0 0 0 2(01) 0 1 0 1 0 1 1 0 0 1 11 - - - - - 3(10) 1 0 0 1 1 0 1 0 1 0 1 00 2 01 3 10 10 00 01 11 10 00 01 11 10 00 11 01 Co po minimalizacji metoda Karnaugha daje się przedstawić: Y1=Q1, Y2=Q2 D1=Q1(X1'X2)'+X1X2' D1=Q1(X1X2')'+X1'X2

... zobacz całą notatkę

Komentarze użytkowników (0)