To tylko jedna z 6 stron tej notatki. Zaloguj się aby zobaczyć ten dokument.

Zobacz

całą notatkę

Temat: Układy kombinacyjne: kodery , multipleksery i demultipleksery.

Cel ćwiczenia

Ćwiczenie ma na celu praktyczne zapoznanie studentów z budową, działaniem, właściwościami oraz syntezą podstawowych układów kombinacyjnych, takich jak: kodery, multipleksery oraz demultipleksery.

Wstęp teoretyczny

Układ kombinacyjny jest jednym z rodzajów układów cyfrowych. Charakteryzuje się tym, że stan wyjść zależy wyłącznie od stanu wejść; stan wyjść opisują funkcje boolowskie - w przeciwieństwie do układów sekwencyjnych, których stan wyjść zależy od stanu wejść oraz od poprzedniego stanu wyjść. Układy kombinacyjne:

• Komutatory - multiplekser, demultiplekser • Konwertery kodów - koder, dekoder, transkoder • Bloki arytmetyczne - sumator, komparator, ALU

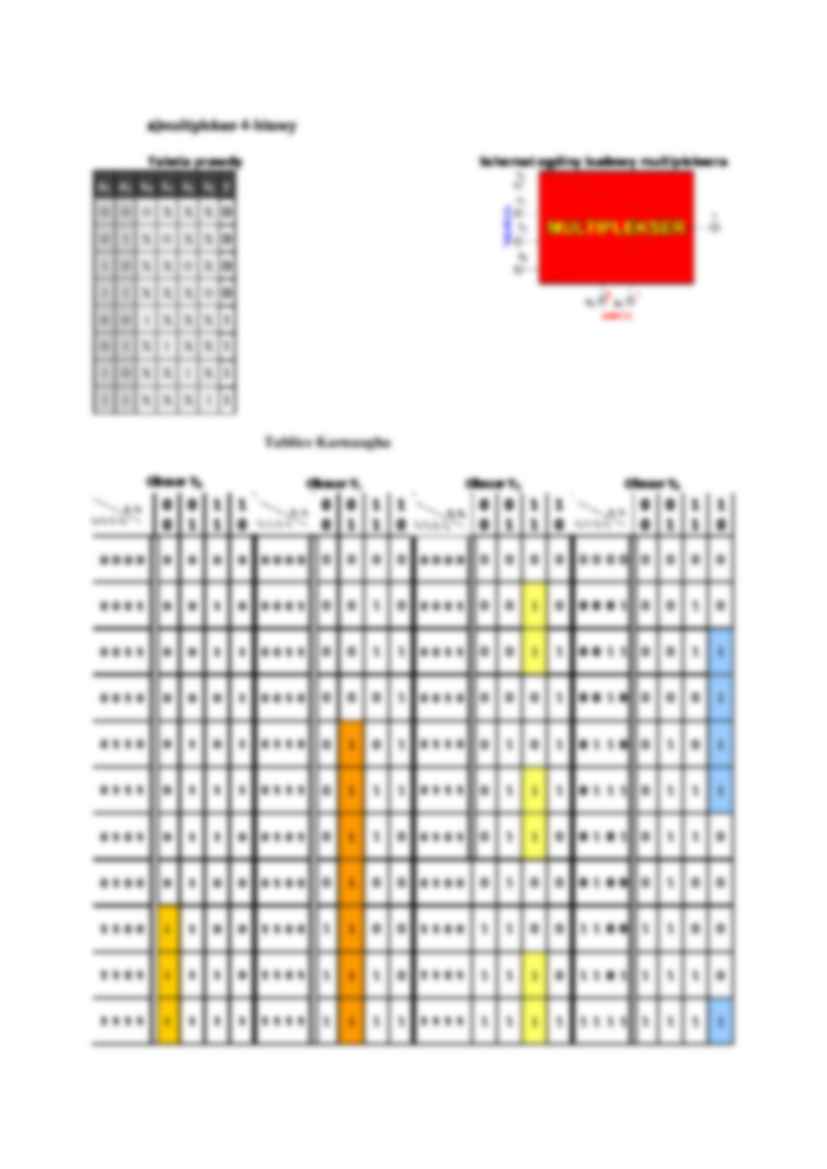

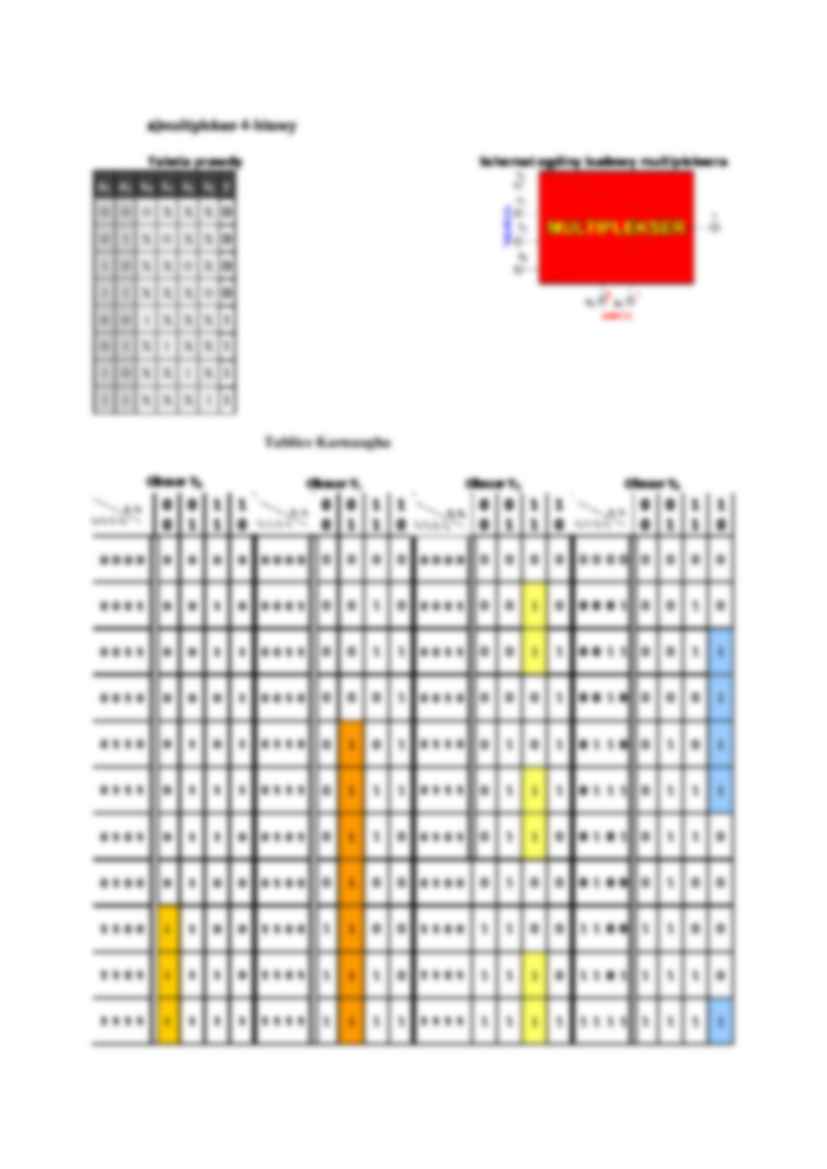

Multiplekser jest układem cyfrowym posiadającym n wejść danych, jedno wyjście y oraz wejścia adresowe. Na wyjściu y pojawia się stan wejścia danych, którego numer podany został na wejścia adresowe. Przykładowy projekt dotyczy układu z czterema wejściami danych D0, D1, D2, D3, z jednym wyjściem Y oraz dwoma wejściami adresowymi A i B.

Demultiplekser jest elementem cyfrowym, który przesyła dane z wejścia na jedno z wyjść, którego numer określa stan wejść adresowych. Pełni on zatem rolę przeciwną do multipleksera. Przykładowy demultiplekser będzie posiadał jedno wejście danych G, cztery wyjścia Y0, Y1, Y2, Y3 oraz dwa wejścia adresowe A i B.

Koder bitu parzystości-Bit parzystości umożliwia pewną ochronę transmisji danych przed błędami.. W tym projekcie naszym zadaniem jest stworzenie sieci logicznej, która generuje bit parzystości dla słowa 4-bitowego. Sieć będzie posiadała 4 wejścia, na które podajemy kolejne bity informacyjne, oraz jedno wyjście, na którym pojawia się bit parzystości. 3. Realizowane ćwiczenia

a)multiplekser 4-bitowy

Tabela prawdy Schemat ogólny budowy multipleksera a1

a2

x0

x1

x2

x2

y 0

0

0

X

X

X

0 0

1

X

0

X

X

0

1

0

X

X

0

X

0 1

1

X

X

X

0

0 0

0

1

X

X

... zobacz całą notatkę

Komentarze użytkowników (0)