To tylko jedna z 6 stron tej notatki. Zaloguj się aby zobaczyć ten dokument.

Zobacz

całą notatkę

Handkiewicz Andrzej. Notatka składa się z 6 stron.

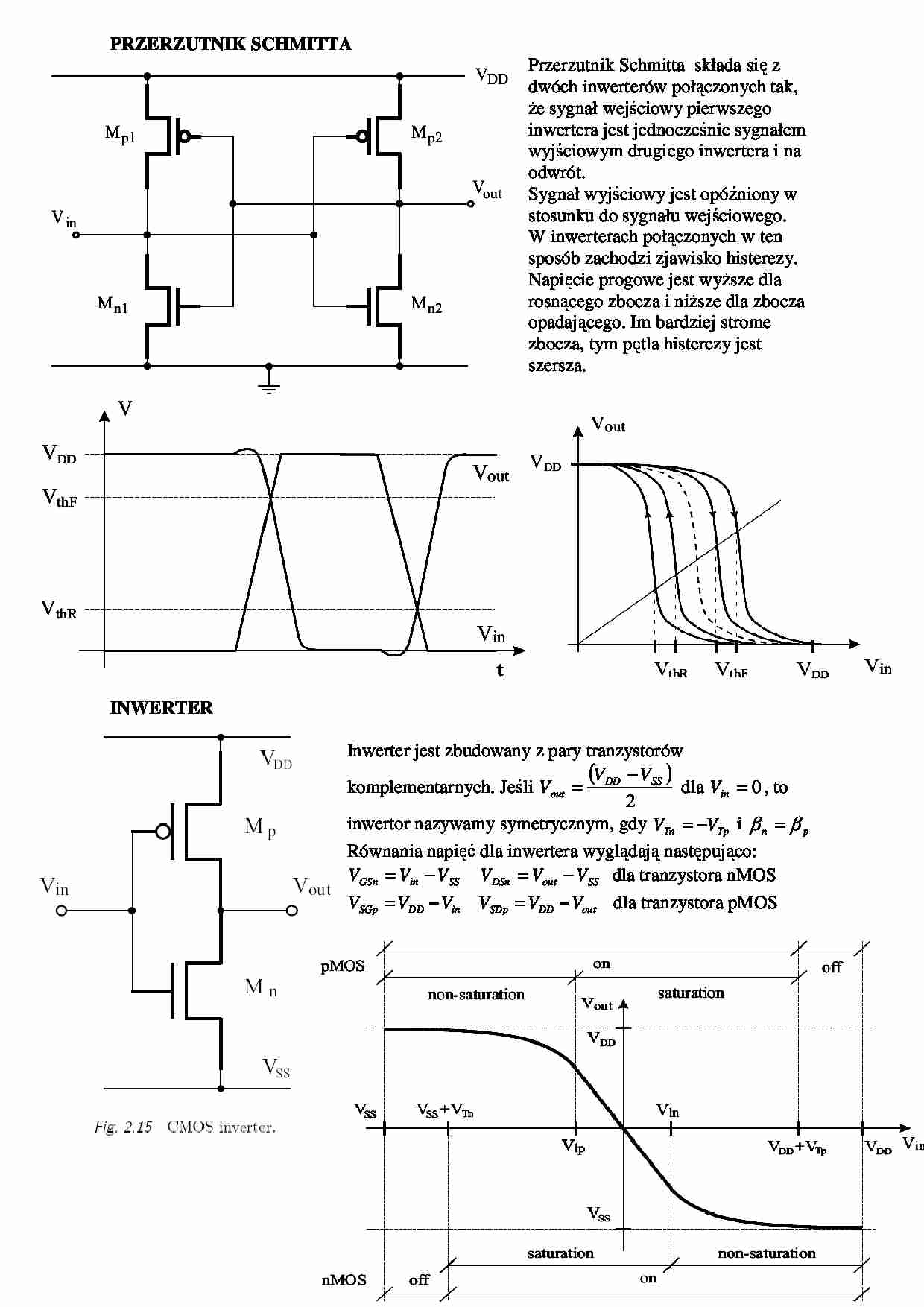

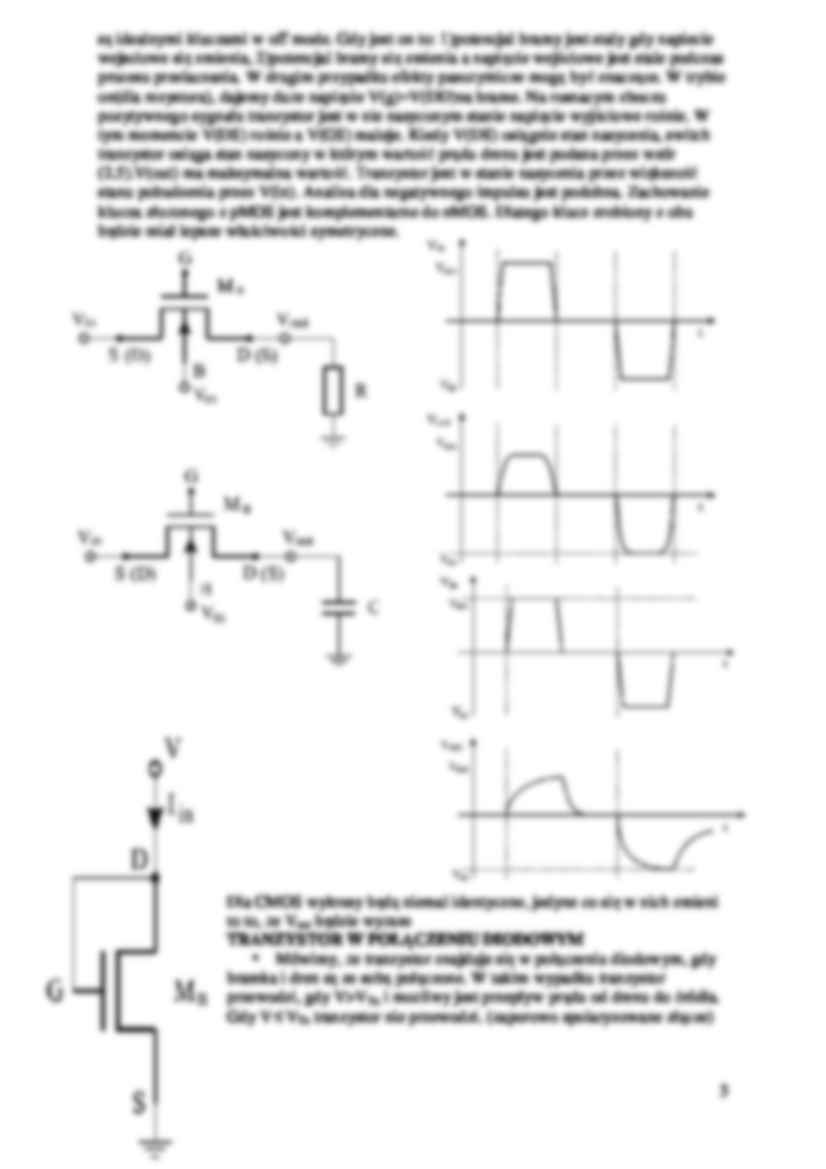

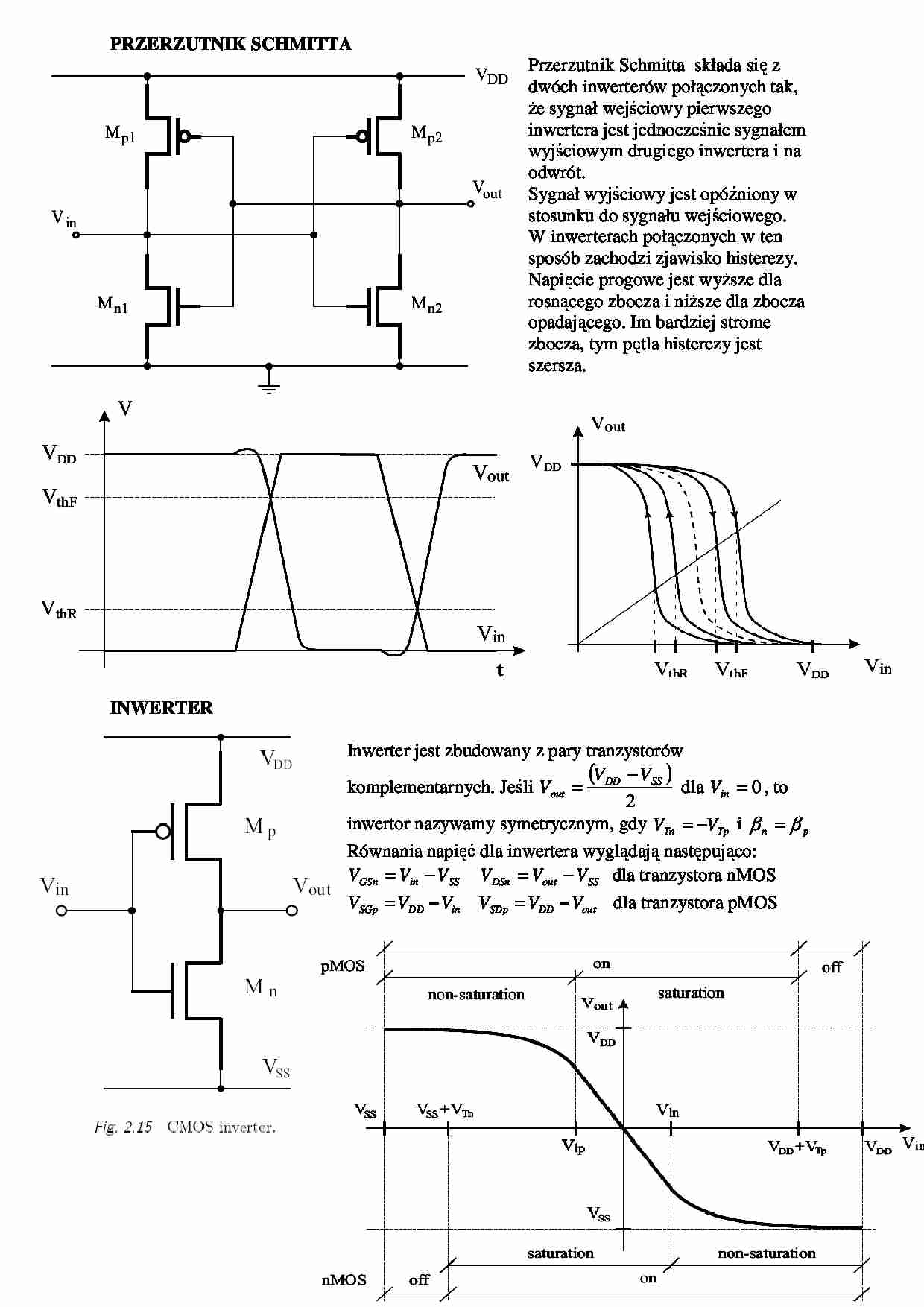

1 PRZERZUTNIK SCHMITTA Przerzutnik Schmitta składa się z dwóch inwerterów połączonych tak, e sygnał wejściowy pierwszego inwertera jest jednocześnie sygnałem wyjściowym drugiego inwertera i na odwrót. Sygnał wyjściowy jest opóźniony w stosunku do sygnału wejściowego. W inwerterach połączonych w ten sposób zachodzi zjawisko histerezy. Napięcie progowe jest wy sze dla rosnącego zbocza i ni sze dla zbocza opadającego. Im bardziej strome zbocza, tym pętla histerezy jest szersza. INWERTER Inwerter jest zbudowany z pary tranzystorów komplementarnych. Jeśli ( ) 2 SS DD out V V V − = dla 0 = in V , to inwertor nazywamy symetrycznym, gdy Tp Tn V V − = i p n β β = Równania napięć dla inwertera wyglądają następująco: SS in GSn V V V − = SS out DSn V V V − = dla tranzystora nMOS in DD SGp V V V − = out DD SDp V V V − = dla tranzystora pMOS 2 Charakterystykę inwertora mo na podzielić na 5 obszarów (w zale ności od tego w jakim stanie są oba tranzystory). 1. ( ) sat SDp SDp Tn GSn Tn SS SS in V V V V V V V V , 0 , : , ≤ = + ∈ 3. ( ) sat SDp SDp sat DSn DSn Ln Lp in V V V V V V V , , , : , ∈ 4. ( ) sat DSn DSn Tp SGp Tp DD Ln in V V V V V V V V , , : , ≤ − + ∈ 5. ( ) sat DSn DSn Tn SGp DD Tp DD in V V V V V V V V , 0 , : , ≤ = − 0). Otwarty tranzystor MOS mo emy traktować jako zwarcie, w związku z tym wyjście Vout zwarte jest do zasilania, Vout=VDD czyli stan wysoki (log. 1), co stanowi negację Vin. Gdy na wejściu Vin pojawi się stan wysoki, wtedy tranzystor Mn przewodzi, czyli zawiera wyjście Vout do masy. Vout=VSS, czyli stan niski (log.0) co stanowi negację Vin. Charskterystyka przej

(…)

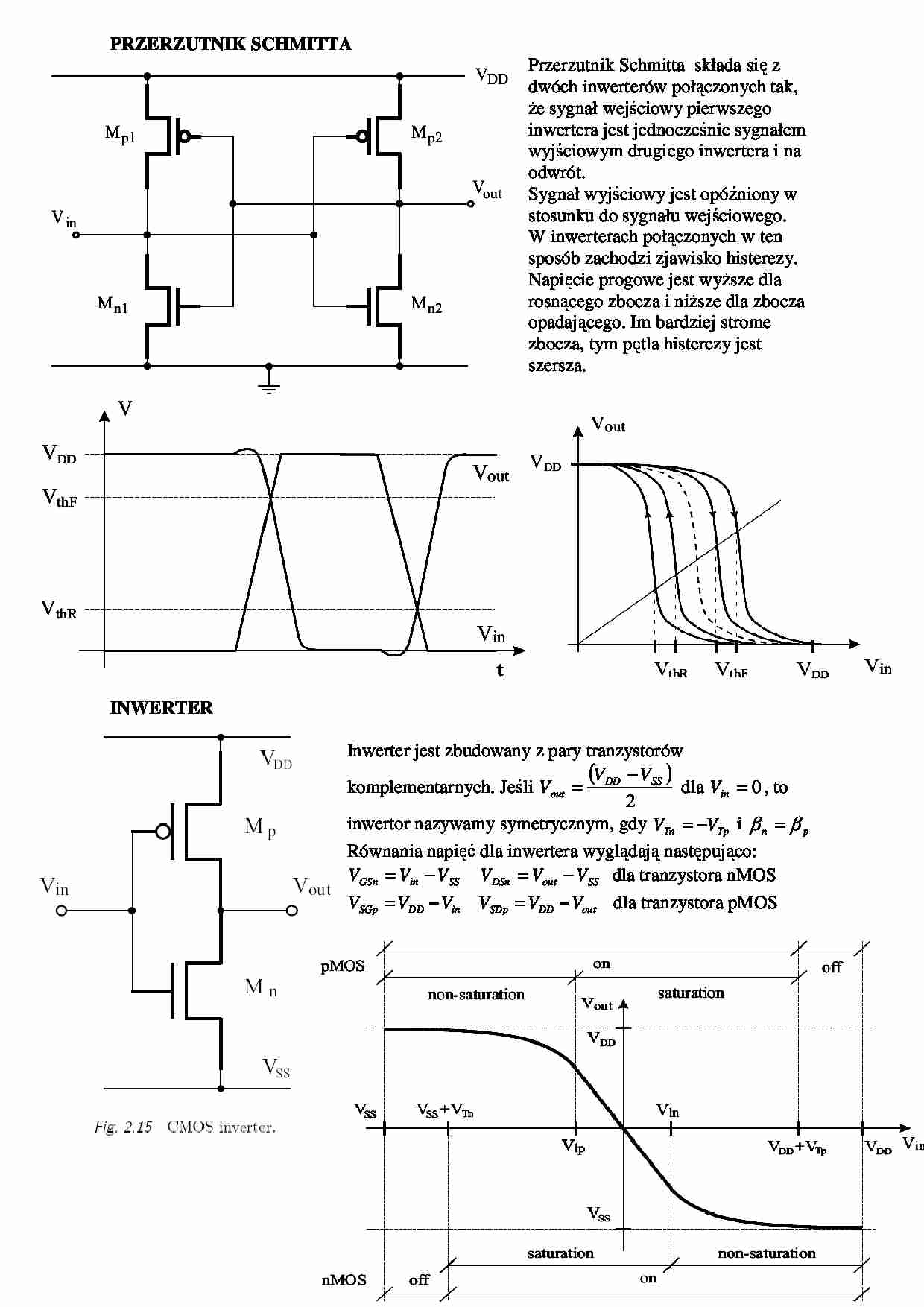

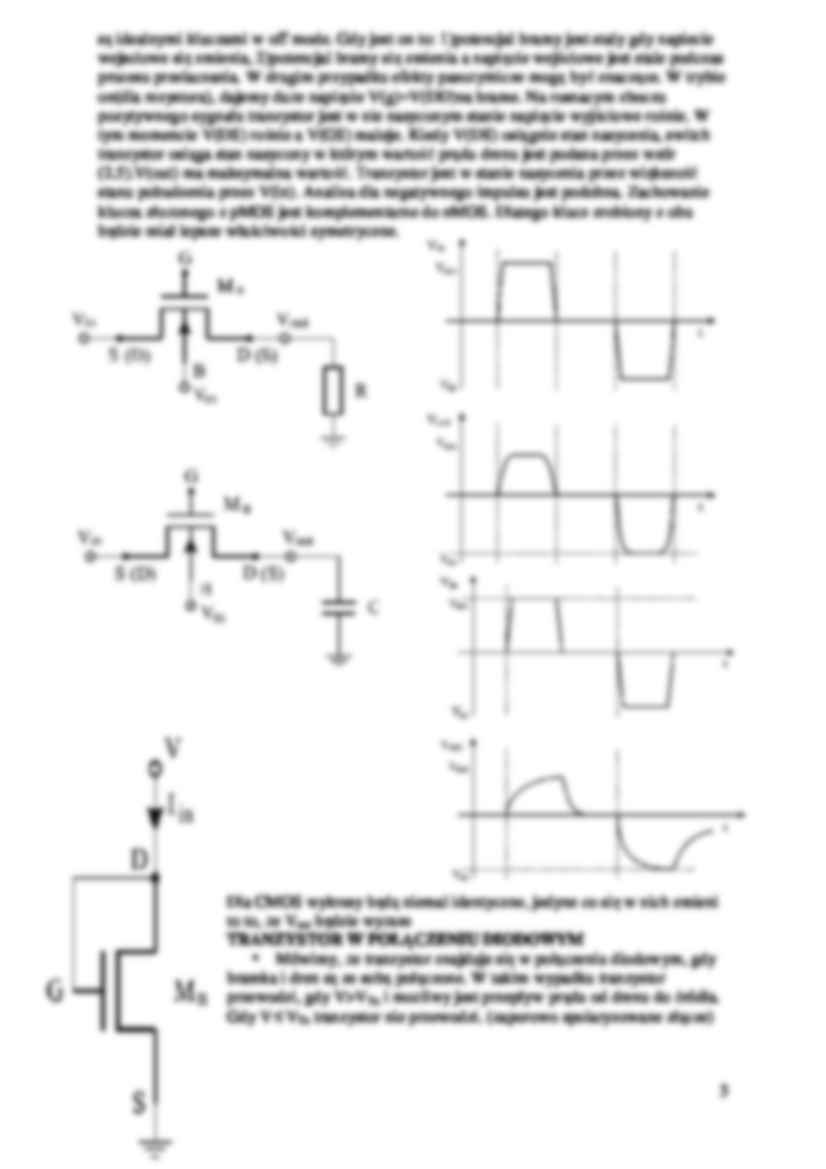

… mode. Gdy jest on to: 1)potencjal bramy jest staly gdy napiecie

wejsciowe się zmienia, 2)potencjal bramy się zmienia a napięcie wejściowe jest stale podczas

procesu przelaczania. W drugim przypadku efekty paso ytnicze mogą być znaczące. W trybie

on(dla rezystora), dajemy du e napięcie V(g)=V(DD)na brame. Na rosnacym zboczu

pozytywnego sygnału tranzystor jest w nie nasyconym stanie napięcie wyjściowe…

… napięcia wejściowego która mo e być reprezentowana jako

logiczne”0”

ࢂࡵࡴ - najmniejsza wartość napięcia wejściowego która mo e być reprezentowana jako

logiczna”1”

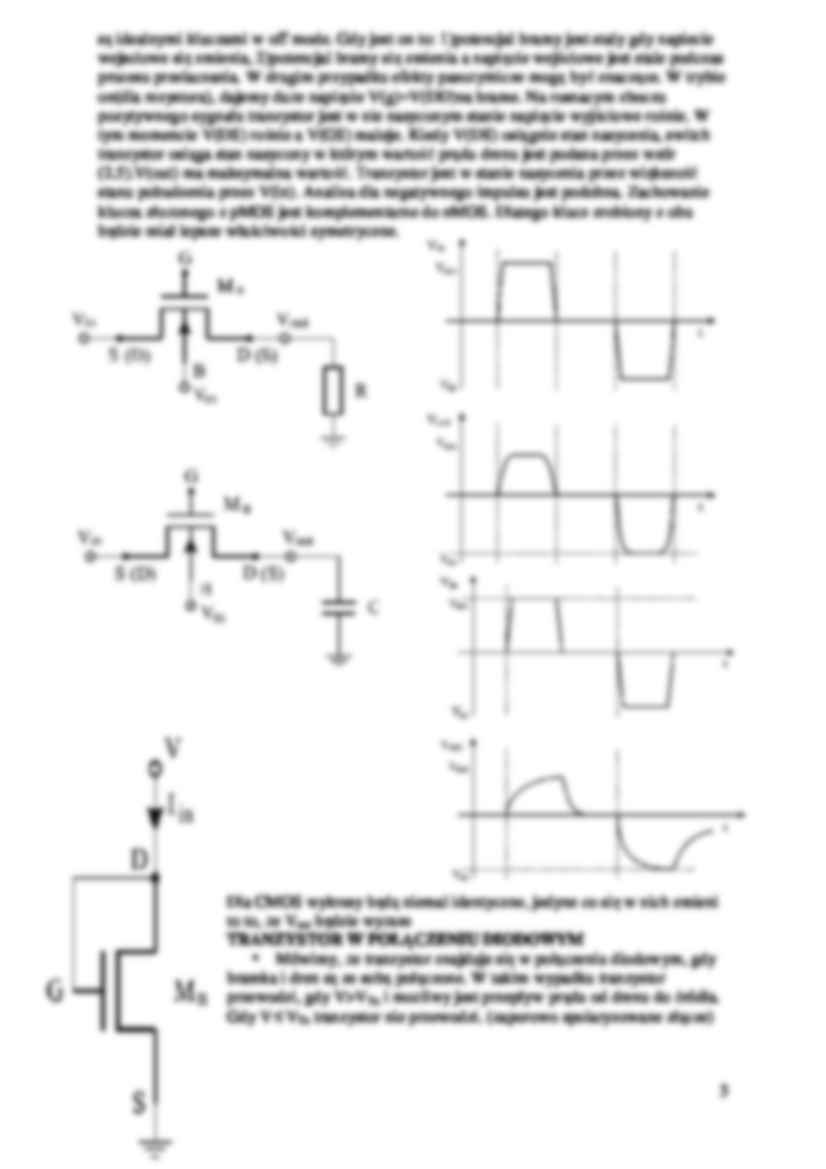

ࢂࢀࢃ - napięcie progowe – jest definiowane jako punkt na charakterystyce przejściowej gdzie

ࢂࡵ ൌ ࢂࡻࢁࢀ . Oba tranzystory są nasycone w tym samym punkcie, więc ࡵࡰ ൌ ࡵࡰ .

TRANZYSTOR JAKO KLUCZ

Posiada dwa tryby: przewodzenie (nie- i nasycenie…

... zobacz całą notatkę

Komentarze użytkowników (0)